# **Combinational Logic**

Rab Nawaz Khan Jadoon

Department of Computer Science

DCS

COMSATS Institute of Information Technology Lecturer COMSATS Lahore

Pakistan

**Digital Logic and Computer Design**

# Combinational logic

## Design Procedures

- Starts from the verbal outline of the problem and ends in a logic circuit diagram.

- The procedure involves the following step,

- The problem is stated.

- Input and required output variables are determined.

- Assigned the variables letter symbols.

- Make the truth table.

- The simplified Boolean functions for each output is obtained.

- The logic diagram is drawn.

## Decoder

- A decoder is a digital circuit that detects the presence of a specified combination of bits (code) on its inputs and indicates the presence of that code by a specified output level.

- A decoder has n input lines to handle n bits and from one to 2<sup>n</sup> output lines to indicate the presence of one or more n-bit combinations. Or

- It is a combinational circuit that converts binary information from n input lines to a maximum of 2<sup>n</sup> unique output lines

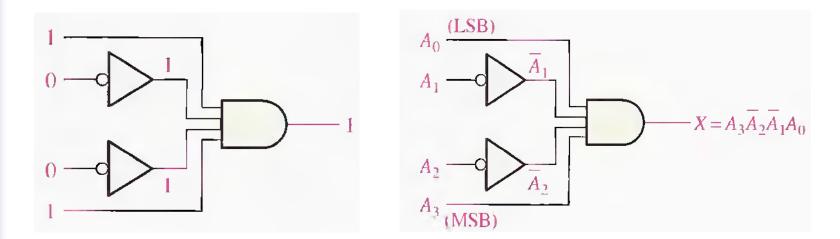

- Suppose you need to determine when a binary 1001 occurs on the inputs of a digital circuit.

- An AND gate can be used as the basic decoding element because it produces a HIGH output only when all of its inputs are HIGH.

- Decoding is necessary in applications such as data multiplexing, 7 segment display and memory address decoding.

- A decoder that contains enable inputs is also known as a decoder-demultiplexer.

- A decoder is a device which does the reverse of an encoder, undoing the encoding so that the original information can be retrieved.

- Therefore, you must make sure that all of the inputs to the AND gate are HIGH when the binary number 1001 occurs.

- this can be done by inverting the two middle bits (the Os), as shown in Figure,

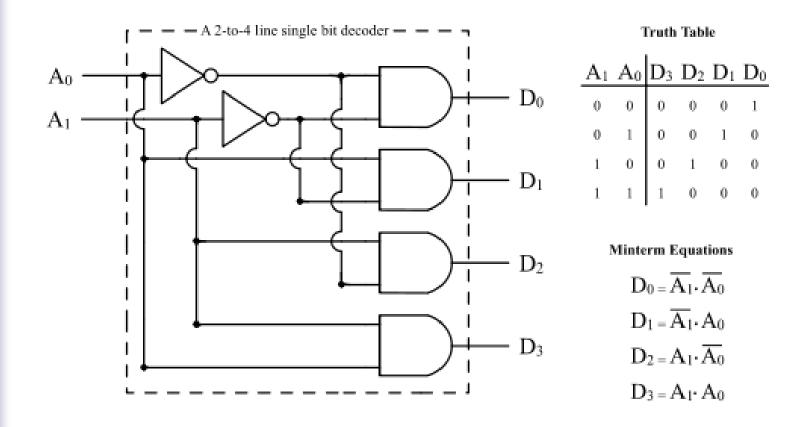

## 2 to 4 line single bit decoder

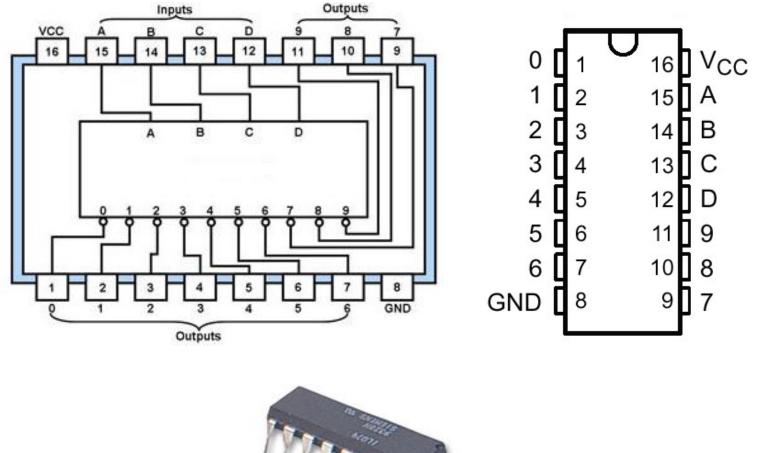

### The 4-Bit Decoder

- In order to decode all possible combinations of four bits, sixteen decoding gates are required (2<sup>4</sup> = 16).

- This type of decoder is commonly called either a 4line-to-16-line decoder because there are four inputs and sixteen outputs.

- 1-of-16 decoder because for any given code on the inputs, one of the sixteen outputs is activated.

- A list of the sixteen binary codes and their corresponding decoding functions is given in Table on next slide.

Decoder

| DECIMAL BINARY INPUTS |                |                       | DECODING              | 1  | OUTPUTS                                                    |   |   |   |   |   |    |   |   | and a |   |    |    |    |    |    |    |

|-----------------------|----------------|-----------------------|-----------------------|----|------------------------------------------------------------|---|---|---|---|---|----|---|---|-------|---|----|----|----|----|----|----|

| DIGIT                 | A <sub>3</sub> | <b>A</b> <sub>2</sub> | <i>A</i> <sub>1</sub> | Ao | FUNCTION                                                   | 0 | 1 | 2 | 3 | 4 | 5  | 6 | 7 | 8     | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 0                     | 0              | 0                     | 0                     | 0  | $\overline{A}_3\overline{A}_2\overline{A}_1\overline{A}_0$ | 0 | 1 | 1 | 1 | l | 1  | 1 | 1 | 1     | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 1                     | 0              | 0                     | 0                     | 1  | $\overline{A}_3\overline{A}_2\overline{A}_1A_0$            | 1 | 0 | 1 | 1 | 1 | 1  | 1 | 1 | 1     | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 2                     | 0              | 0                     | - 1                   | 0  | $\overline{A}_3\overline{A}_2A_1\overline{A}_0$            | 1 | 1 | 0 | 1 | 1 | 1  | 1 | 1 | 1     | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 3                     | 0              | 0                     | 1                     | 1  | $\overline{A}_3\overline{A}_2A_1A_0$                       | 1 | 1 | 1 | 0 | 1 | 1- | 1 | 1 | 1     | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 4                     | 0              | 1                     | 0                     | 0  | $\overline{A}_3 A_2 \overline{A}_1 \overline{A}_0$         | 1 | 1 | 1 | 1 | 0 | 1  | 1 | 1 | 1     | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 5                     | 0              | 1                     | 0                     | 1  | $\overline{A}_{3}A_{2}\overline{A}_{1}A_{0}$               | 1 | 1 | 1 | 1 | 1 | 0  | 1 | 1 | 1     | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 6                     | 0              | 1                     | 1                     | 0  | $\overline{A}_{3}A_{2}A_{1}\overline{A}_{0}$               | 1 | 1 | 1 | 1 | 1 | 1  | 0 | 1 | 1     | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 7                     | 0              | 1                     | 1                     | 1  | $\overline{A}_{3}A_{2}A_{1}A_{0}$                          | 1 | 1 | 1 | 1 | 1 | 1  | 1 | 0 | 1     | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 8                     | 1              | 0                     | 0                     | 0  | $A_3\overline{A}_2\overline{A}_1\overline{A}_0$            | 1 | 1 | 1 | 1 | 1 | 1  | 1 | 1 | 0     | 1 | 1  | 1  | 1  | 1  | 1  | 1  |

| 9                     | 1              | 0                     | 0                     | 1  | $A_3\overline{A}_2\overline{A}_1A_0$                       | 1 | 1 | 1 | 1 | 1 | 1  | 1 | 1 | 1     | 0 | 1  | 1  | 1  | 1  | 1  | 1  |

| 10                    | 1              | 0                     | 1                     | 0  | $A_3\overline{A}_2A_1\overline{A}_0$                       | 1 | 1 | 1 | 1 | 1 | 1  | 1 | 1 | 1     | 1 | 0  | 1  | 1  | 1  | 1  | 1  |

| 11                    | 1              | 0                     | 1                     | 1  | $A_3\overline{A}_2A_1A_0$                                  | 1 | 1 | 1 | 1 | 1 | 1  | 1 | 1 | l     | l | 1  | 0  | 1  | 1  | 1  | 1  |

| 12                    | 1              | 1                     | 0                     | 0  | $A_3 A_2 \overline{A}_1 \overline{A}_0$                    | 1 | 1 | 1 | 1 | 1 | 1  | 1 | 1 | 1     | l | 1  | 1  | 0  | 1  | 1  | 1  |

| 13                    | 1              | 1                     | 0                     | 1  | $A_3 A_2 \overline{A}_1 A_0$                               | 1 | 1 | 1 | 1 | 1 | 1  | 1 | 1 | 1     | 1 | 1  | 1  | 1  | 0  | l  | 1  |

| 14                    | 1              | 1                     | 1                     | 0  | $A_3 A_2 A_1 \overline{A}_0$                               | 1 | 1 | l | 1 | 1 | 1  | 1 | 1 | 1     | 1 | 1  | 1  | 1  | 1  | 0  | 1  |

| 15                    | 1              | l                     | 1                     | 1  | $A_3A_2A_1A_0$                                             | 1 | 1 | 1 | 1 | 1 | 1  | 1 | 1 | 1     | 1 | 1  | l  | 1  | 1  | 1  | 0  |

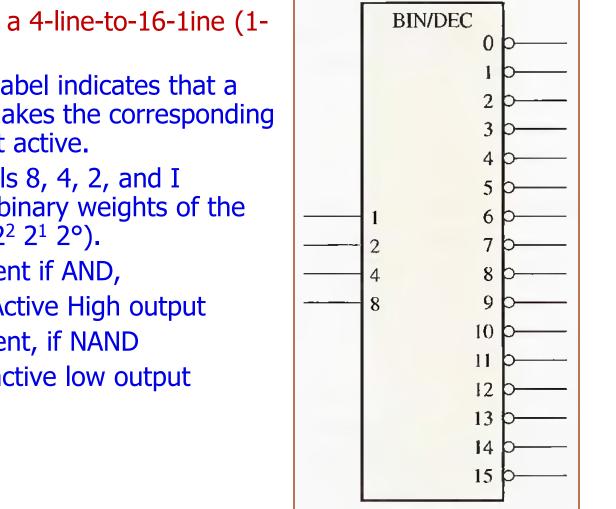

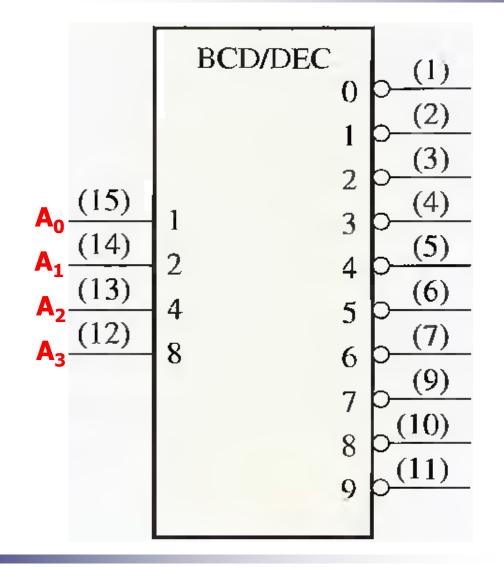

- A logic symbol for a 4-line-to-16-1ine (1of-16) decoder.

- The BIN/DEC label indicates that a binary input makes the corresponding decimal output active.

- The input labels 8, 4, 2, and I represent the binary weights of the input bits (2<sup>3</sup> 2<sup>2</sup> 2<sup>1</sup> 2<sup>o</sup>).

- Decoder element if AND,

- Output is Active High output

- Decoder element, if NAND

- Output is active low output

### The BCD-to-Decimal Decoder

- The BCD-to-decimal decoder converts each BCD code (8421 code) into one of ten possible decimal digit indications.

- Only ten decoding gates are required because the BCD code represents only the ten decimal digits 0 through 9.

- A list of the ten BCD codes and their corresponding decoding functions is given in Table on the next slide,

| DECIMAL |                       | BCDC           | DECODING              |                |                                                            |

|---------|-----------------------|----------------|-----------------------|----------------|------------------------------------------------------------|

| DIGIT   | <b>A</b> <sub>3</sub> | A <sub>2</sub> | <i>A</i> <sub>1</sub> | A <sub>0</sub> | FUNCTION                                                   |

| 0       | 0                     | 0              | 0                     | 0              | $\overline{A}_3\overline{A}_2\overline{A}_1\overline{A}_0$ |

| 1       | 0                     | 0              | 0                     | 1              | $\overline{A}_{3}\overline{A}_{2}\overline{A}_{1}A_{0}$    |

| 2       | 0                     | 0              | 1                     | 0              | $\overline{A}_3\overline{A}_2A_1\overline{A}_0$            |

| 3       | 0                     | 0              | 1                     | 1              | $\overline{A}_{3}\overline{A}_{2}A_{1}A_{0}$               |

| 4       | 0                     | 1              | 0                     | 0              | $\overline{A}_{3}A_{2}\overline{A}_{1}\overline{A}_{0}$    |

| 5       | 0                     | 1              | 0                     | 1              | $\overline{A}_{3}A_{2}\overline{A}_{1}A_{0}$               |

| 6       | 0                     | 1              | 1                     | 0              | $\overline{A}_{3}A_{2}A_{1}\overline{A}_{0}$               |

| 7       | 0                     | 1              | 1                     | 1              | $\overline{A}_{3}A_{2}A_{1}A_{0}$                          |

| 8       | 1                     | 0              | 0                     | 0              | $A_3\overline{A}_2\overline{A}_1\overline{A}_0$            |

| 9       | 1                     | 0              | 0                     | 1              | $A_3\overline{A}_2\overline{A}_1A_0$                       |

COMSATS

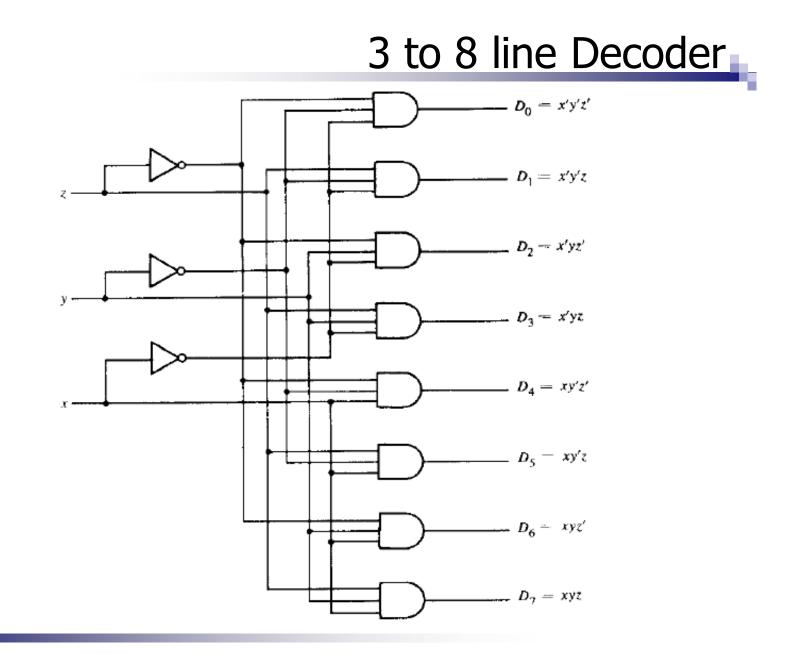

| Tru      | Truth Table of a 3-to-8-Line Decoder |   |                |   |    |       |       |                |                |       |  |

|----------|--------------------------------------|---|----------------|---|----|-------|-------|----------------|----------------|-------|--|

|          | Inputs                               |   |                |   |    | Out   | puts  |                |                |       |  |

| <u>x</u> | y                                    | Z | D <sub>c</sub> |   | Dz | $D_3$ | $D_4$ | D <sub>5</sub> | D <sub>6</sub> | $D_7$ |  |

| 0        | 0                                    | 0 | 1              | 0 | 0  | 0     | 0     | 0              | 0              | 0     |  |

| 0        | D                                    | 1 | 0              | 1 | 0  | 0     | 0     | 0              | 0              | 0     |  |

| 0        | 1                                    | 0 | 0              | 0 | 1  | 0     | 0     | 0              | 0              | 0     |  |

| 0        | 1                                    | 1 | 0              | 0 | 0  | 1     | 0     | 0              | 0              | 0     |  |

| 1        | 0                                    | 0 | 0              | 0 | 0  | 0     | 1     | 0              | 0              | 0     |  |

| 1        | 0                                    | 1 | 0              | 0 | 0  | 0     | 0     | 1              | 0              | 0     |  |

| 1        | 1                                    | 0 | 0              | 0 | 0  | 0     | 0     | 0              | 1              | 0     |  |

| 1        | 1                                    | 1 | 0              | 0 | 0  | 0     | 0     | 0              | 0              | 1     |  |

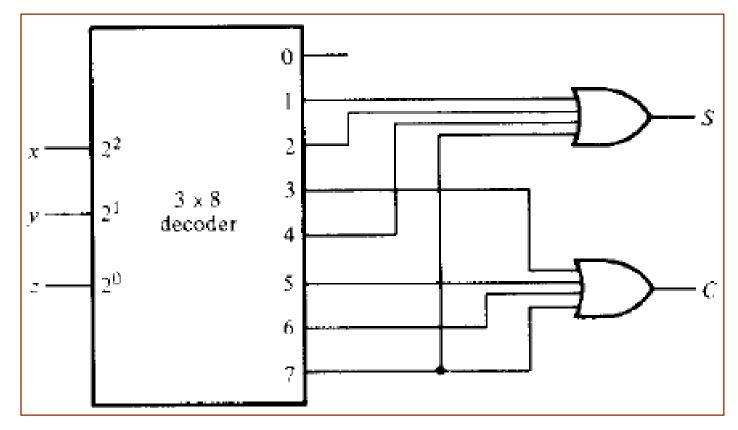

## Combinational Logic Implementation

The procedure for implementing a combinational circuit by means of a decoder and OR Gates requires that the boolean functions for the circuit be expressed in SOP.

- This form can easily be obtained from the truth table.

- A decoder is then chosen that generates all the minterms of the n input variables.

- The inputs to each OR gate are selected from the decoder outputs according to the minterm list in each function.

#### Problem:

Implement a full adder circuit with a decoder and two OR gates.

#### Solution:

From the truth table of full adder,

$$S(x, y, z) = \Sigma(1, 2, 4, 7)$$

$$C(x, y, z) = \Sigma(3, 5, 6, 7)$$

Since there are three inputs and a total of eight minterms, we need a 3 to 8 line decoder.

# Implementation of a full adder with a decoder

The decoder method can be used to implement any combination Circuit. However its implementation must be compared with all others Possible implementation to determine the best solution.

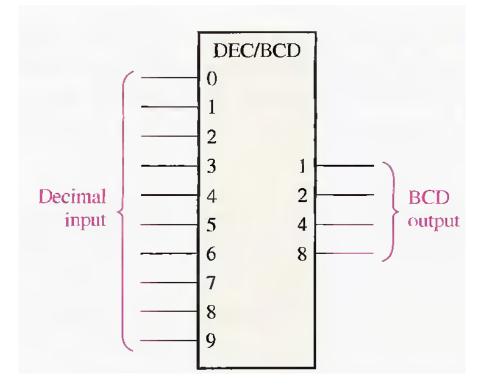

- An encoder is a combinational logic circuit that essentially performs a "reverse" decoder.

- An encoder accepts an active level on one of its inputs representing a digit, such as a decimal or octal digit, and converts it to a coded output, such as BCD or binary.

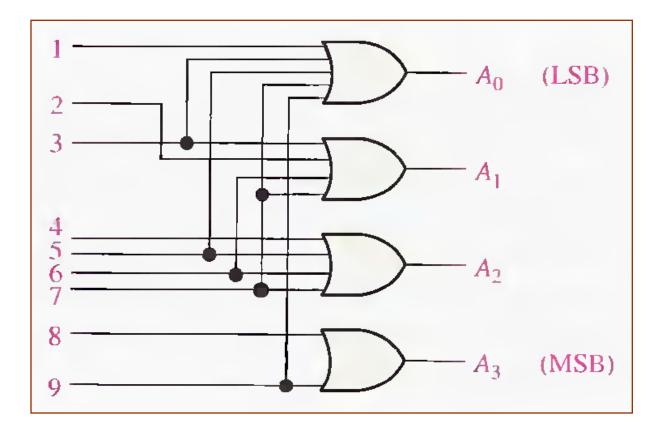

This type of encoder has ten inputs-one for each decimal digit-and four outputs corresponding to the BCD code, as shown in Figure below,

|               |                | BCD                   | CODE           |                |

|---------------|----------------|-----------------------|----------------|----------------|

| DECIMAL DIGIT | A <sub>3</sub> | <b>A</b> <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |

| 0             | 0              | 0                     | 0              | 0              |

| 1             | 0              | 0                     | 0              | 1              |

| 2             | 0              | 0                     | 1              | 0              |

| 3             | 0              | 0                     | 1              | 1              |

| 4             | 0              | 1                     | 0              | 0              |

| 5             | 0              | 1                     | 0              | 1              |

| 6             | 0              | 1                     | 1              | 0              |

| 7             | 0              | 1                     | 1              | 1              |

| 8             | 1              | 0                     | 0              | 0              |

| 9             | 1              | 0                     | 0              | 1              |

- From this table you can determine the relationship between each BCD bit and the decimal digits in order to analyze the logic.

- For instance, the most significant bit of the BCD code, A<sub>3</sub>, is always a 1 for decimal digit 8 or 9.

- An OR expression for bit A<sub>3</sub> in terms of the decimal digits can therefore be written as,

- $A_3 = 8 + 9$

- Bit A<sub>2</sub> is always a I for decimal digit 4, 5, 6 or 7 and can be expressed as an OR function as follows:

- Bit A<sub>1</sub> is always a 1 for decimal digit 2, 3, 6, or 7 and can be expressed as

- $\bullet A_1 = 2 + 3 + 6 + 7$

- Finally. A<sub>0</sub> is always a1 for decimal digit 1. 3. 5. 7. or

9. The expression for A<sub>0</sub> is

- A<sub>0</sub>=1+3+5+7+9

- Now let's implement the logic circuitry required for encoding each decimal digit to a BCD code by using the logic expressions just developed.

- It is simply a matter of ORing the appropriate decimal digit input lines to form each BCD output.

- When a HIGH appears on one of the decimal digit input lines, the appropriate levels occur on the four BCD output lines.

- For instance, if input line 9 is HIGH (assuming all other input lines are LOW), this condition will produce a HIGH on outputs A<sub>0</sub> and A<sub>3</sub> and LOWs on outputs A<sub>1</sub> and A<sub>2</sub>, which is the BCD code (1001) for decimal 9.